# インタコネクション技術の概要

Outline of Interconnection Technologies

岩田 穆

# 1. 集積エレクトロニクスの進歩

## 1.1 アーキテクチャ

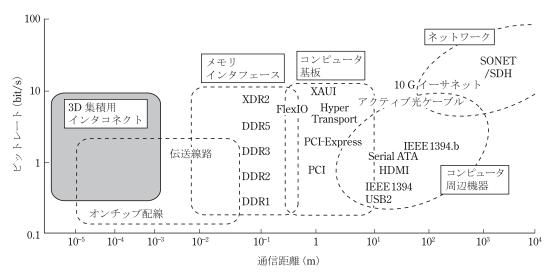

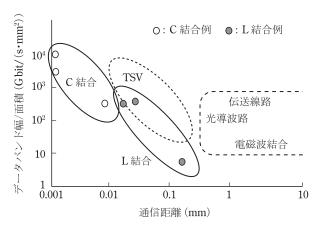

マイクロプロセッサのビット数の拡大とともにクロック周波数が上昇したが、3 GHz 程度で壁にぶつかり、並列処理によるマルチコアが主流になった。更に超並列分散処理による能力向上に向かっている。光通信は 1980年代から光ファイバの普及により、長距離の大容量通信から始まり、家庭用の Fiber to the Home (FTTH)、コンピュータの装置間接続、ボード間通信と、短距離の領域にも適用が拡大してきた。図1にデータバンド幅と通信距離を軸として、既存のインタコネクション技術を示す。これからはプロセッサとメモリ間、分散プロセッサ間の情報転送など、より短距離のインタコネクション技術が一層重要になっている。

## 1.2 集積技術

20世紀後半から微細デバイスと回路の進歩により、チップに集積されるトランジスタ数は2年で2倍の速度で増加してきた(ムーアの法則).また、高速クロックで動作するディジタル回路が主流となった.21世紀になり、漏れ電流による消費電力増加、チップ上の配線の伝搬遅延時間が増加、微細デバイスの製造コストが急激に増加するため、ムーアの法則に沿った進展が飽和している。そこで、集積規模の拡大のために、微細化のみに依存しないマルチチップ技術が種々開発された。現在は、チップに貫通電極を形成して前工程でチップを積層する三次元集積技術が活発に開発されている(1).

岩田 穆 正員:フェロー (株)エイアールテック

E-mail iwa@a-r-tec.jp Atsushi IWATA, Fellow (A-R-Tec Corp., Higashihiroshima-shi, 739-0005 Ianan)

電子情報通信学会誌 Vol.94 No.12 pp.1022-1026 2011 年 12 月 ©電子情報通信学会 2011

## 1.3 三次元集積

既存の三次元積層はチップをボンディングワイヤで接続する方法である。接続のためにチップサイズを変える必要があり,チップ周辺しか接続できない。そこで,三次元積層したチップ間を垂直方向に接続する技術が注目されている。図1に示すように三次元集積のために積層チップ間の超短距離( $1\mu$ m $\sim$ 1 mm)のインタコネクション技術が鍵になる。これを用いると配線長は大幅に短縮され,寄生容量も低減するので,高速化と低電力化が図れる。任意の位置でチップ間を接続できるので,膨大な本数の配線,複雑な接続にも対応できる。三次元集積により,プロセッサとメモリ間のデータバンド幅を上げて,処理能力を向上するというニーズは顕在化しており,データバンド幅 100 Gbit/s 以上が必要となっている。

# 2. インタコネクションの種類と特長

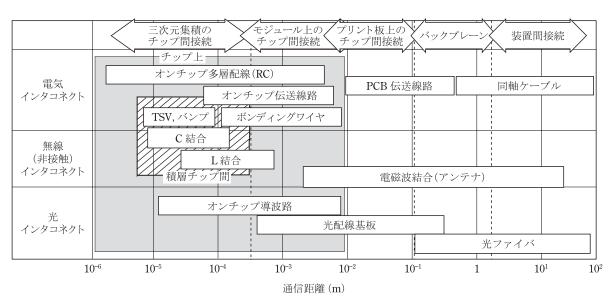

接続距離を横軸にして短距離のインタコネクション技術の適用領域を図2に示す.

## 2.1 電気インタコネクト

#### (1) RC 線路

チップ上の細い配線で長距離を接続する場合は RC 線路になり、帯域が制限される。この制限を解決するため、 $0.4\,\mu$ m のラインアンドスペースの RC 線路で 3 Gbit/s の信号を  $10\,\mathrm{mm}$  の距離伝送する回路技術が開発された。消費電力は  $6\,\mathrm{mW}$  である  $^{(2)}$ .

#### (2) 伝送線路

チップ上配線でギガヘルツ以上の広帯域を得るには伝送線路が必要である。線路設計でインピーダンス整合、伝送損特性を良くするには  $1\sim10~\mu m$  程度の断面サイズが必要となり、高密度の集積には向かない。

図1 各種インタコネクション技術のビットレート対通信距離 光通信,インターネット,コンピュータ,ディジタル機器において,各種のインタコネクション技術によって,10 Gbit/s のビットレートが実現されてきた.現在,三次元集積のための超短距離のインタコネクションが注目されている.

図2 短距離インタコネクション技術の適用領域 短距離のインタコネクションには Si 貫通ビア (TSV), 静電 (C) 結合, 電磁 (L) 結合, 電磁波結合, 光結合があり, それぞれ通信距離に対する適用領域, 特長を有している.

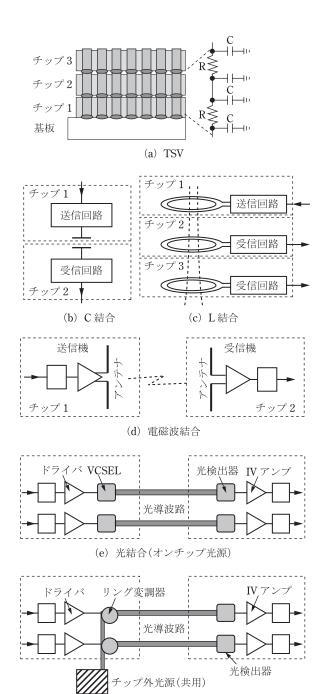

#### (3) Si 貫通ビア (TSV)

TSV 間をバンプで接続した三次元集積の構造例とその等価回路を図3(a)に示す. TSV は導電性のあるSi 基板との間に大きな寄生容量を持ち,これがビットレートを5 Gbit/s 程度に制限する. TSV の径と間隔の縮小,アスペクト比の拡大,寄生容量低減が性能を決める. 各種の TSV 形成とチップ積層の工程があるが,コスト面からはウェーハで積層する方法が本命とされている.

# 2.2 無線(非接触)インタコネクト

#### (1) 静電結合 (C 結合)

キャパシタによる静電結合の原理的な構造を図3(b)

に示す.チップ表面に形成した  $10\sim100~\mu m$  の小形電極を Face to face で近接させキャパシタを形成する.このキャパシタ(C)で情報を伝えると,Gbit/s オーダのデータ転送速度が得られる (3)。 実用的な伝送特性を得るには電極間距離は電極サイズの  $1/10~\mu m$  オーダ)にする必要であるので, $2~\mu m$  チップを Face to face で積層することは可能であるが, $3~\mu m$  チップ以上の積層には TSV との併用が必要である.また,この方式はチップ間の電位変動が通信に影響するため対策が必要である.

#### (2) 電磁結合 (L 結合)

各チップ上の多層配線によるインダクタ(L)対で形成したマイクロトランスによる通信であり、その原理を図3(c)に示す.電磁誘導の法則により一次側電流の微分波形が二次側に誘導電圧として発生する.データ用の送受信回路とクロック用送受信回路を設けた、同期方式が高速で、誤り率も低いので、よく使われる<sup>(4)</sup>. Lサイ

図3 三次元集積用インタコネクション技術の構成 (b), (c), (d)では通常の集積回路のデバイスで実現でき、積層は接着でよいのでコスト的に有利である. (a)では Si 貫通ビア (TSV) 形成と接続の工程, (e), (f)では発光、受光素子、導波路などの光部品の製造と集積化の工程が必要である.

(f) 光結合(外部光源)

ズの 1/2 の距離で 0.1 の結合係数が得られるので 3 層以上のチップ間を接続できる.L の小形化にはチップの薄層化が必要である.磁界は広がるので,隣接して L を配置するとクロストークのため誤動作する可能性がある.L の配置,駆動のタイミングの工夫によりこのクロストークを抑圧する必要がある.L サイズ  $100\,\mu\text{m}$ , L 間の距離  $20\sim50\,\mu\text{m}$  で,データ転送速度  $2\,\text{Gbit/s}$  が代表的な性能である.低電力設計では  $1\,\text{bit}$  転送のエネルギーは  $0.1\,\text{pJ}$  が,高速設計ではビットレート  $11\,\text{Gbit/s}$  が実証された  $^{(5),(6)}$  L 間距離と位置ずれは L サイズの 20% 程度まで許容される.

#### (3) 電磁波結合

図 3(d) に示すように,送受信機とアンテナを用いて GHz 以上の変調電磁波を使うので,1 mm 以上の長距離 に適する.遠方界による電磁波結合でメリットが出る距離は信号帯域 10 GHz の場合 0.5 mm 以上である (7) . また,近傍界を用いるとより短い距離に使うこともできる.変調方式には振幅変調,位相変調,広帯域パルス伝送も有望である.ガウシアンモノサイクルパルスを用いて, $1\sim5 \text{ GHz}$  帯域でビットレート 1.16 Gbit/s が確認されている (8) . この方式はアンテナの小形化が必須の課題である.

## 2.3 光インタコネクション

電気信号を光に変えて伝送して. 受信回路で電気に戻 す(図3(e)). 光は伝送速度が速く, 導波路伝搬ではエ ネルギーを小断面積に閉じ込めることができ、また、遮 光によりクロストークを抑圧可能である. 現在. 10~100 m の装置間接続、スーパコンピュータの超高周 波クロックの供給, 超広帯域データバスに使われてい る. 10 cm~1 m のボード間接続, 1~10 cm のボード内 チップ間接続のために Ge を用いた光検出器を Si チップ に搭載した 10 Gbit/s の 1 チップ光トランシーバも開発 された<sup>(9)</sup>. 将来の光電融合集積では光素子をチップ上に 置いて、電気配線を短くして容量充放電による消費電力 を削減できる. 導波路の光伝搬速度は光速/屈折率 (c/ n) であり、230 mm/ns と高速であるので、受信光から 変換された小振幅の電圧を論理振幅に増幅する高速アン プの動作速度と電力消費が支配的になる. 図3(e)に示 すオンチップ垂直キャビティ面発光レーザ (VCSEL) を光源として直接変調するのが理想であるが、化合物半 導体 VCSEL の Si チップへの集積化は当面難しいので、 図3(f)に示す外部光をチップ内で分岐して、変調して 通信する方法もある. 光導波路にはSi 材料による導波 路. 有機導波路による光配線板. 曲げと分岐導波路には ミラーやグレーティングが適している. また. フォト ニッククリスタルを用いた導波路, 共振器, フィルタな ども研究されている.

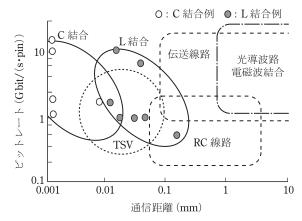

# 3. 各種インタコネクションの性能比較

チップ内,チップ間,ボード間,装置間という階層 で、情報転送の距離に対する適合性が重要である。デー タレート, 伝送路断面積, 送受信回路面積, 通信エネル ギーなどを比較評価する. 集積化インタコネクション技 術のビットレート (ピン当り) 対通信距離を図4に示 す. オンチップの RC 線路や TSV では、抵抗と寄生容 量による帯域制限で決まる. 伝送線路にすれば 10 Gbit/s 以上は実現できる. C 結合, L 結合では 100 μm 以下の 短距離で10 Gbit/s という高い値が実証されている. 将 来は光結合で 1 mm 以上の中距離で 10 Gbit/s 以上が実 現される可能性がある. 面積当りデータバンド幅の通信 距離依存性を図5に示す. C 結合と TSV で1 Tbit/(s・ mm²)以上と大きい値を実現できる. 距離 10 μm 以下の 場合, C 結合で 10 Tbit/(s·mm<sup>2</sup>)という最高値が実現で き, 距離 10~100 μm では TSV が効率的になる. L 結 合は通信距離の2倍程度のサイズのLが必要であるの

図 4 ビットレート対通信距離 静電 (C) 結合は  $1\sim10~\mu m$  の 距離で、電磁 (L) 結合は  $10\sim100~\mu m$  の距離で、 $1\sim10~Gbit/s$  の 高いビットレートが得られている。Si 貫通ビア(TSV)では、10~Gbit/s を得るには電力消費を要する。

図5 面積当りのデータバンド幅対通信距離 面積当りのデータバンド幅では静電結合が最も高効率を示す. 電磁結合ではLのサイズが必要なため,効率が低い.

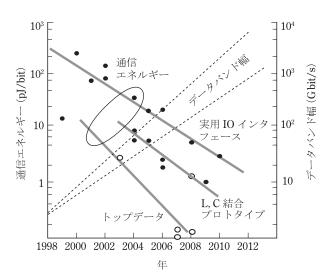

で、数百 Gbit/( $s \cdot mm^2$ )以下になる。距離 1 mm 以上では伝送線路,電磁波,光によるインタコネクションの適用領域になるが,チップ面積は送受信回路と伝送路との接続部の面積で決まり, $1 T bit/(s \cdot mm^2)$ 以下になるであろう。通信に必要なエネルギーの年次推移を図 6 に示す。ビット当りの通信エネルギーは消費電力/ビットレートと等しく, $1 p J = 1 m W/(1 G b i t \cdot s)$  を目標として技術開発が進められた。電気による入出力インタフェースでは 3 p J 程度が最高の仕様であるが,近年,短距離通信で,0.1 p J/b i t というトップデータが報告され,大規模マルチプロセッサの試作では 1 p J 以下が得られている。このように,各種インタコネクション技術の特長は,距離に依存して発揮されるので,大規模なシステムでは,複数の技術の組合せも必要となると思われる.

# 4. 三次元集積の現状と課題

## (1) 貫通ビア三次元集積

TSV を用いた 2 Gbit チップを 4 枚三次元集積した 8 GbitDRAM が開発されており、実装面積で 70% の節約ができる。また、三次元集積イメージセンサも生産されている。製造工程、回路アーキテクチャ、テスト技術などを一層向上させて、プロセッサとメモリを集積して、大幅な性能向上を狙うドリームチップのプロジェクトなどが進められている (10).

## (2) C 結合三次元集積

2 チップをフェースツーフェースに接着し、距離約 1  $\mu$ m で接続した C 結合デモシステムが試作された。  $8 \times 8$   $\mu$ m の電極でクロック周波数 1.7 GHz、消費電力 0.15

図 6 通信エネルギーの年次推移 インタコネクションに要するビット当りエネルギーは 2年で 1/2 になり、実用レベルの IO インタフェースで 3 pJ/bit に迫ってきた、静電結合、電磁結合ではトップデータで 0.1 pJ/bit が実証され、実用レベルで 1 pJ/bit 以下が期待できる。

$\mu$ W/(Gbit/s) +1.6  $\mu$ W, 面積当りのデータレート 22 Mbit/(s・ $\mu$ m²) を達成している。クロック用には 20×20  $\mu$ m の電極を用い 1.8 GHz を送る。誤り率は  $10^{-12}$  以下が確認されている (11).

#### (3) L 結合三次元集積

プリント基板にフェースダウンでバンプ実装した8コアプロセッサチップの上に SRAM チップをフェースアップで積層し、両チップを通して L 結合でデータ転送するシステムが試作された  $^{(12)}$ . SRAM の電源(1.2 V)はボンディングワイヤで供給される. 通信距離は  $120\,\mu\text{m}$ , クロック周波数  $600\,\text{MHz}$ , データバンド幅は  $19.2\,\text{Gbit/s}$ ( $600\,\text{MHz} \times 16\,\text{ch} \times 2$ ),ビット当りエネルギーは  $1\,\text{pJ/bit}$  であり,データレート当りの面積は  $0.15\,\text{mm}^2$ /(Gbit/s)であり,誤りは  $10^{-14}$  である.

# (4) 光結合三次元集積

基礎レベルで多くの取組みがある. 光源を Si 基板上に形成するのが最終形である. また, 光導波路と回路を形成した Si 基板と, 発光素子を形成した化合物半導体基板を積層する三次元集積が検討されている. 空間伝搬の光で接続した三次元集積も研究されている.

#### (5) 複合インタコネクト三次元集積

接続距離に応じて、C 結合と L 結合を複合して三次元集積する方法、光と C 結合を複合化して、高感度の非 Si 光センサを Si チップに非接触接続する方法などが考えられる。また、医療用センシングなどでは内視鏡カプセルのように、体内外間の無線通信も重要になっている。将来、このような技術により、人間の目より小さい体積  $1 \, \mathrm{cm}^3$  で目と脳の一部の機能を三次元集積回路として実現できるであろう。

# 5. む す び

集積規模の拡大には、三次元構造が必須になった。C 結合は、数 $\mu$ m 程度の短距離接続では速度、電力、面積について最も効率が良い。L 結合は  $0.1\sim1$  mm の距離で、3 層以上のチップを接続できる。面積は大きいが、高速、低電力動作が実現できる。電磁波結合は距離 1 mm $\sim10$  cm の接続ができる。光インタコネクションは、三次元集積技術として新材料、新デバイスの開拓が必要である。将来は、各方式を複合化して、脳のような複雑な三次元集積システムが実現されるであろう。

#### 文献

- (1) J.U. Knickerbocker, C.S. Patel, P.S. Andry, C.K. Tsang, L.P. Buchwalter, E.J. Sprogis, H. Gan, R.R. Horton, R.J. Polastre, S.L. Wright, and J.M. Cotte, "3-D silicon integration and silicon packaging technology using silicon through-vias," IEEE J. Solid-State Circuits, vol. 41, no. 8, pp. 1718-1725, 2006.

- (2) D. Schinkel, E. Mensink, E. Klumperink, E. van Tuijl, and B. Nauta, "A 3-Gb/s/ch transceiver for 10-mm uninterrupted RC-limited global on-chip interconnects," IEEE J. Solid-State Circuits, vol. 41, no. 1, pp. 297-306, 2006.

- (3) K. Kanda, D.D. Antono, K. Ishida, H. Kawaguchi, T. Kuroda, and T. Sakurai, "1.27 Gb/s/ch 3 mW/pin wireless superconnect (WSC) interface scheme," ISSCC Dig. of Tech. Papers, no. 10.7, pp. 186-187, 2003.

- (4) 岩田 穆, "三次元集積のためのインダクタ対による無線インタ コネクション," 信学誌, vol. 90, no. 10, pp. 864-870, Oct. 2007.

- (5) N. Miura, H. Ishikuro, T. Sakurai, and T. Kuroda, "A 0.14 pJ/b inductive-coupling inter-chip data transceiver with digitally-controlled precise pulse shaping," ISSCC Dig. of Tech. Papers, no. 20.2, pp. 358-359, 2007.

- (6) N. Miura, Y. Kohama, Y. Sugimori, H. Ishikuro, T. Sakurai, and T. Kuroda, "An 11 Gb/s inductive-coupling link with burst transmission," ISSCC Dig. of Tech. Papers, no. 15.7, pp. 298-299, 2008.

- (7) J. Rabaey, F. Burghardt, Y. Chee, D. Chen, L. De Nardis, S. Gambini, D. Guermandi, M. Mark, and N. Pletcher, "Short distance wireless and its opportunities," IEEE Dallas/CAS Workshop on Design, Applications, Integration and Software, pp. 1-6, 2006.

- (9) D. Kucharski, D. Guckenberger, G. Masini, S. Abdalla, J. Witzens, and S. Sahni, "10 Gb/s 15 mW optical receiver with integrated germanium photodetector and hybrid inductor peaking in 0.13 μm SOI CMOS technology," ISSCC Dig. of Tech. Papers, no. 20.1, pp. 298-299, 2010.

- (10) M. Kada, "Development of functionally innovative 3D-integrated circuit (dream chip) technology/high-density 3D-integration technology for multifunctional devices," IEEE International Conference on 3D System Integration, pp. 1-6, 2009.

- (11) A. Fazzi, R. Canegallo, L. Ciccarelli, L. Magagni, F. Natali, E. Jung, P. Rolandi, and R. Guerrieri, "3-D capacitive interconnections with monoand bi-directional capabilities," IEEE J. Solid-State Circuits, vol. 43, no. 1, pp. 275-284, 2008.

- (12) K. Niitsu, Y. Shimazaki, Y. Sugimori, Y. Kohama, K. Kasuga, I. Nonomura, M. Saen, S. Komatsu, K. Osada, N. Irie, T. Hattori, A. Hasegawa, and T. Kuroda, "An inductive-coupling link for 3D integration of a 90 nm CMOS processor and a 65 nm CMOS SRAM," ISSCC Dig. of Tech. Papers, no. 28.7, pp. 479-480, 2009.

(平成 23 年 6 月 30 日受付 平成 23 年 7 月 13 日最終受付)

# 岩田 穆 (正員:フェロー)

昭 43 名大・工・電子卒,昭 45 同大学院修士課程了。同年日本電信電話公社(現 NTT)通信研究所入社。通信用アナログ集積回路の研究開発に従事。平 7 広島大教授。本会集積回路専門委員長。著書「VLSI 工学一基礎・設計編一」(本会編,コロナ社)。平 6 全国発明表彰特許庁長官賞,平 19 IEEE Trans. on Circuits and Systems Darlington Best Paper Award 各受賞、工博、